Journal of Computer Science 10 (5): 723-728, 2014 ISSN: 1549-3636 © 2014 Science Publications doi:10.3844/jcssp.2014.723.728 Published Online 10 (5) 2014 (http://www.thescipub.com/jcs.toc)

## DESIGN OF OPTIMAL CARRY SKIP ADDER AND CARRY SKIP BCD ADDER USING REVERSIBLE LOGIC GATES

### <sup>1</sup>Praveena Murugesan and <sup>2</sup>Thanushkodi Keppanagounder

<sup>1</sup>Department of ECE, Anna University, Tamilnadu, India <sup>2</sup>Akshaya College of Engineering and Technology, Coimbatore, Tamilnadu, India

Received 2013-10-08; Revised 2013-11-24; Accepted 2013-12-26

#### ABSTRACT

Reversible logic circuits have the ability to produce zero power dissipation which has found its importance in quantum computing, optical computing and low power digital circuits. The study presents improved and efficient reversible logic circuits for carry skip adder and carry skip BCD adder. The performance of the proposed architecture is better than the existing works in terms of gate count, garbage outputs and constant inputs. This design forms the basis for different quantum ALU and embedded processors.

Keywords:Low Power Circuits, Reversible Logic, Binary Coded Decimal Adder, Carry Skip Adder, Optical Computing

#### **1. INTRODUCTION**

Landauer (1961) proved that conventional combinational logic gates like AND OR disperse heat for every quantity of information that is destroyed while performing their operation regardless of the technology that is employed for accomplishing the circuit. According to his principle the energy dispersed for irreversible bit operation is given by KT ln2 (K-Boltzmann's constant and T-absolute temperature of the environment). Thus when the complexity of the circuit increases the energy dissipation becomes the major drawback factor.

The fundamental difference between irreversible circuits and reversible circuits is that the later doesn't lose any information. Bennett (1973) showed that only by applying the principle of reversibility to the circuits the zero power dissipation is possible. Thus reversibility concept will become an extremely important property in all future circuit design.

In computers, the most common numbering system is binary number system. However there is a need for Binary coded decimal number system in commercial, financial and internet based applications. This major importance arises from the fact that decimal numbers like 1.101 cannot be exactly represented with high accuracy in binary format and processing of these data is done using decimal arithmetic software (Cowlishaw, 2003). These factors specify the need for BCD in computers but it has its own drawback too. It is slower by 100 to 1000 times the binary arithmetic. This highlights the importance of both binary and BCD number system in their respective applications.

Adders are the basic building blocks in many computational units. There are different types of adders and the most commonly used adders are ripple carry adder, carry skip adder and carry look-ahead adder.

In the ripple carry adder the carry bit has to propagate through all the adder stages and this increases the delay of the circuit. By the introduction of carry look-ahead adders the carry bit is computed in parallel fashion, but they employ a large number of gates for computations. However, in this carry skip adder the propagation time is reduced by skipping over the group of adder stages (Islam *et al.*, 2009) and presents hardware and performance compromise

Corresponding Author: Praveena Murugesan, Department of ECE, Anna University, Tamilnadu, India

between carry look-ahead adder and ripple carry adder. So, faster adder circuits for binary and binary coded decimal have been investigated for several decades. The study continues the tradition by using reversible logic circuits for the design of carry skip adder and carry skip BCD adder. When compared in terms of gate count, garbage output and constant input, the proposed architecture performs better than the existing architectures.

#### **1.1. Basic Denotations**

#### 1.1.1. Reversible Gate

A Reversible gate is an m-input, n-output (denoted by  $m \times n$ ) circuit that produces unique output pattern (Haghparast *et al.*, 2008a) for each possible input pattern. A gate with i inputs and o outputs is said to be reversible if and only if i = o and there should be one to one correspondence between its inputs and outputs.

#### 1.1.2. Garbage Output

The output of the reversible gate that is not used as a primary output or as input to other gates is called the garbage output. In short the unused output of a reversible gate (or circuit) is the garbage output (s). These garbage outputs are needed in the circuit to maintain the reversibility concept. It has a clear influence on the performance of the circuit and therefore should be minimized as much as possible. For example when the  $4\times4$  HNG gate (Haghparast *et al.*, 2008b) is used to perform the operation of full adder, the output vectors P = A and Q = B are the garbage output produced to preserve reversibility.

#### 1.1.3. Quantum Cost

Quantum Cost of the circuit is calculated by knowing the number of basic reversible gates (gates of which cost is already known) needed to realize the circuit.

#### **1.1.4.** Constant Input

Input which is added to a  $n \times n$  function for making it reversible is named as constant input. These input lines in the input side are either set to zero or one so as to bring the needed result. For example, consider the Feynman gate in which when any one input of the input line is set at constant 0, then the copy of an input bit is obtained and when any one input of the input line is at constant 1, then the inverted input bit is obtained.

# Science Publications

#### 1.1.5. Restrictions on Reversible logic synthesis

In designing reversible circuits Fan-out and Feedback or loops are strictly limited (Feynman, 1985). However these can be attained by the usage of additional gates like FG and BVF.

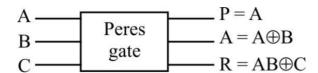

#### 1.1.6. Reversible Peres Gate (PG)

The 3×3 (Peres, 1985) is described as follows: Input vector  $I_v = (A, B, C)$  and output vector  $O_v = (P = A, Q = A \oplus B, R = AB \oplus C)$ . Block diagram of Peres is depicted in **Fig. 1**. Peres gate is the mixture of Feynman gate and Toffoli (1980) and this can implement operations like AND EX-OR. In this proposed design PG gate is used for performing AND operation.

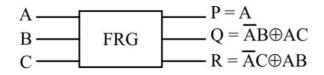

#### 1.1.7. Reversible Fredkin Gate (FRG)

Input and output vectors for  $3\times3$  FRG (Fredkin and Toffoli, 1982) is defined as follows:  $I_v = (A, B, C)$  and  $O_v = (P = A, Q = B \oplus AC, R = C \oplus AB)$  FRG gate is depicted in **Fig. 2** and it is used in (Bruce *et al.*, 2002) to construct ripple carry and carry skip adder circuits. This gate is used in the proposed designs for performing both AND and OR operation. This AND-OR output is obtained at output R.

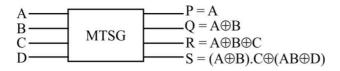

#### 1.1.8. Reversible MTSG Gate

Modified TSG (MTSG) gate is a 4×4 reversible gate (Biswas *et al.*, 2008a) with following input and output vectors,  $I_v = (A, B, C, D)$  and  $O_v = (P = A, Q = A \oplus B, R$ =  $A \oplus B \oplus C$  and  $S = (A \oplus B)$ .  $C \oplus (AB \oplus D)$ . This MTSG gate in **Fig. 3** can be used to realize a full adder by providing constant '0' at the input D.Quantum cost of reversible MTSG gate is 6 which is lower than 13 of TSG gate (Thapliyal *et al.*, 2006).

This gate is used in the design so as to produce the sum, carry and the propagate output of the inputs.

#### 1.1.9. MPS Gate

The reversible  $5 \times 5$  MPS gate is further simplified and redrawn in **Fig. 4** and this works as a BCD detection and correction gate. This gate for performing the above operation does not use any constant input and produces zero garbage output. This gate detects the input that is greater than 1001 (9) and corrects it with correction factor of 0110 (6) to produce the final BCD output. Praveena Murugesan and Thanushkodi Keppanagounder / Journal of Computer Science 10 (5): 723-728, 2014

Fig. 1. Peres gate

Fig. 2. Fredkin gate

Fig. 3. MTSG gate

| A<br>B<br>C<br>D<br>E<br>MPS | $P = A\overline{B} + \overline{A}BC + B\overline{C} (A \oplus D)$ $Q = A(C+B) + \overline{C}(A\overline{B}D + \overline{A}B\overline{D})$ $R = \overline{A}C(\overline{B}+BE) + A\overline{C}\overline{D} + AC(B+D)$ $S = BC(\overline{A}\oplus D) + \overline{B}(A\oplus D) + AB\overline{C}$ $T = F$ |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Fig. 4. MPS gate

#### 2. MATERIALS AND METHODS

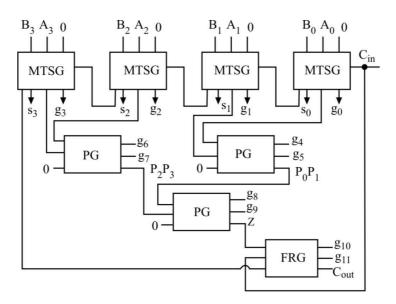

#### 2.1. Proposed Reversible Carry Skip Adder

In the proposed carry skip adder in **Fig. 5**, 4 bit parallel addition is done by the modified TSG (MTSG) gate. The block propagate signal Z is generated using three Peres gate, where  $Z = p_0.p_1.p_2.p_3$  and  $p_0 = A_0 \oplus B_0$ ,  $p_1 = A_1 \oplus B_1$ ,  $p_2 = A_2 \oplus B_2$ ,  $p_3 = A_3 \oplus B_3$ .

Instead of Peres gate, even Toffoli gate can also be used for this purpose. But in this circuit Peres gate is preferred because of lower quantum cost when compared to Toffoli gate (Biswas *et al.*, 2008a). The combined AND-OR function i.e.,  $C_{out} = ZC_{in} + C_4$  is done by the fredkin gate.

The algorithm of the proposed design is as follows:

#### Algorithm:

Reversible Carry-skip-adder (A,B,C<sub>i</sub>)

Input: Input Vectors:  $A = (A_3, A_2, A_1, A_0)$  and  $B=(B_3, B_2, B_1, B_0)$ Carry input :  $C_{in}$

Output:

Output Vectors:

$$S = (C_{out}, S_3, S_2, S_1, S_0)$$

begin

Step1:

Compute propagate bit  $P_i$  for each adder block. for (i = 0 to 3)

$$P_i = A_i \oplus B_i$$

$Z = P_o AND P_1 AND P_2 AND P_3$

Step 2:

Compute  $S_i = A_i \oplus B_i \oplus C_i$  for every adder block using the MTSG gate and  $C_i = (A_i \oplus B_i)$ .  $C_{in} \oplus A_i B_i$  is generated for each adder block.

Step 3:

Evaluate the final carry output,  $C_{out} = ZC_{in}+C_4$ end

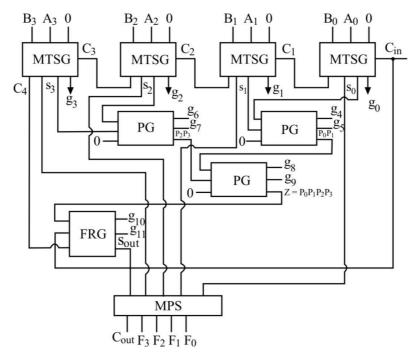

#### 2.2. Proposed Reversible Carry Skip BCD Adder

This proposed adder follows the same base architecture of proposed carry skip adder except that it includes a block for the BCD overflow detection and correction as depicted in **Fig. 6**. MTSG is used for the 4 bit parallel addition and produces the propagate bits ( $P_0$ ,  $P_1$ ,  $P_2$ ,  $P_3$ ) of its input in addition tosum and carry.

The carry skip logic block consists of three peres gate and one fredkin gate. The carry bit  $S_{out}$  is calculated based on the block propagate signal Z, carry in  $C_{in}$  and the most significant full adder carry bit  $C_4$ . i.e.,  $S_{out} = ZC_{in}+C_4$ . The carry skip logic can improve carry propagation if the block propagate signal Z is equal to one. When Z = 1, the carry input  $C_{in}$ propagates to  $S_{out}$  regardless of the carry  $C_4$ . When Z =0 then the carry  $C_4$  propagates to  $C_{out}$  i.e., carry will be generated in ripple carry fashion.

This generation of  $C_4$  will consume time and the AND-OR logic i.e., fredkin gate will wait for generating  $S_{out}$  until  $C_4$  is resolved. Once after obtaining the carry  $S_{out}$  it passes through the MPS gate along with the intermediate sum i.e.,  $(S_3, S_2, S_1, S_0)$ . The single MPS gate acts as a BCD overflow detector and corrector gate. This produces the final BCD sum i.e.,  $(C_{out}, F_3, F_2, F_1 \text{ and } F_0)$ .

Praveena Murugesan and Thanushkodi Keppanagounder / Journal of Computer Science 10 (5): 723-728, 2014

Fig. 5. Proposed carry skip adder

Fig. 6. Proposed carry skip BCD adder

#### **3. RESULTS**

The proposed reversible carry skip adder and reversible carry skip BCD adder circuits can be evaluated in terms of gate counts, constant inputs and garbage outputs produced. **Table 1** depicts the comparative analysis of different reversible carry skip adder circuits.

Evaluation of the proposed reversible carry skip BCD adder can be comprehended easily with the help of **Table 2**.

**Table 1.** Comparison of different carry skip adders

|                      | Gate  | Garbage | Constant |

|----------------------|-------|---------|----------|

| Designs in           | count | outputs | inputs   |

| (Islam et al., 2009) | 14    | 19      | 15       |

| (Bruce et al., 2002) | 24    | 22      | 21       |

| (Lala et al., 2010)  | 22    | 27      | 22       |

| Proposed             | 8     | 12      | 7        |

**Table 2.** Comparisons of reversible carry skip BCD adders

|                                  | Gate  | Garbage | Constant |

|----------------------------------|-------|---------|----------|

| Designs in                       | count | outputs | input    |

| (Biswas et al., 2008b)           | 15    | 14      | 11       |

| (Thapliyal <i>et al.</i> , 2006) | 15    | 27      | 13       |

| (Islam et al., 2009;             | 15    | 14      | 11       |

| Biswas et al., 2008b)            |       |         |          |

| (Islam and Begam, 2008)          | 15    | 36      | 24       |

| (Bhagyalakshmi and               | 13    | 14      | 10       |

| Venkatesha, 2011)                |       |         |          |

| Proposed                         | 9     | 12      | 7        |

#### 4. DISCUSSION

The **Table 1** clearly shows that in (Fredkin and Toffoli, 1982) full adder is constructed using 5 fredkin gates and it uses 4 constant inputs and produces 4 garbage outputs. Hence for 4 bit parallel addition it uses 20 fredkin gates, 16 constant inputs and produces 16 garbage outputs. This implementation in total requires 24 numbers of gates, uses 21 constant inputs and produces 22 garbage outputs.

Lala *et al.* (2010) New Full Adder (NFA) is constructed using 4R gates, uses 4 constant inputs and produces 4 garbage outputs. Therefore in total this circuit uses 22 numbers of gates, uses 22 constant inputs and produces 27 garbage outputs.

Islam *et al.* (2009) parity preserving gates are used for the construction of the circuit. This design is better when compared to the other designs in (Bruce *et al.*, 2002; Lala *et al.*, 2010) but the proposed design performs better than all the existing designs in every parameter.

It is evident from **Table 2** that the optimization parameters of designs in (Thapliyal *et al.*, 2006; Islam and Begam, 2008) are computed with fan-out which in strict sense is restricted in reversible circuits and when reconstructed without fan-out it is sure that all the parameters will increase drastically when compared to the present results. Therefore from **Table 2** it is obvious that the proposed design performs better the existing designs in all parameters.

#### **5. CONCLUSION**

In the study an optimized carry skip adder and carry skip BCD adder are presented. It is clearly found that both circuits are highly optimized in terms of gate count, constant input and garbage output when compared with the existing designs. These optimized parameters will have a direct effect on the total cost of the circuit. These types of adders will be definitely useful in constructing larger computational structures and in future computers.

#### **6. REFERENCES**

- Bennett, C.H., 1973. Logical reversibility of computation. IBM J. Res. Dev., 17: 525-532. DOI: 10.1147/rd.176.0525

- Bhagyalakshmi, H.R. and M.K. Venkatesha, 2011. Optimized design of BCD adder and carry skip BCD adder using reversible logic gates. Int. J. Comput. Sci. Eng., 3: 1439-1449.

- Biswas, A.K., M.M. Hasan, A.R. Chowdhury and H.M.H. Babu, 2008a. Efficient approaches for designing reversible binary coded decimal adders. Microelectron. J., 39: 1693-1703. DOI: 10.1016/j.mejo.2008.04.003.

- Biswas, A.K., M.M. Hasan, M. Hasan, A.R. Chowdhury and M.D. Hafiz *et al.*, 2008b. A novel approach to design BCD adder and carry skip BCD adder. Proceedings of the 21st International Conference on VLSI Design, Jan. 4-8, IEEE Xplore Press, Hyderabad, pp: 566-571. DOI: 10.1109/VLSI.2008.37

- Bruce, J.W., M.A. Thornton, L. Shivakumaraiah, P.S. Kokate and X. Li, 2002. Efficient adder circuits based on a conservative reversible logic. Proceedings of the IEEE 6th Computer Society Annual Symposium VLSI, Apr. 25-26, IEEE Xplore Press, Pittsburgh, PA., pp: 74-79. DOI: 10.1109/ISVLSI.2002.1016879

- Cowlishaw, M.F., 2003. Decimal floating-point Algorism for computers. Proceedings of the 16th IEEE Symposium on Computer Arithmetic, Jun. 15-18, IEEE Xplore Perss, pp: 104-111. DOI: 10.1109/ARITH.2003.1207666

- Feynman, R.P., 1985. Quantum Mechanical Computers.

- Fredkin, E. and E. Toffoli, 1982. Conservative logic. Int. J. Theor. Phys., 21: 219-253. DOI: 10.1007/BF01857727

Praveena Murugesan and Thanushkodi Keppanagounder / Journal of Computer Science 10 (5): 723-728, 2014

- Haghparast, M. and K. Navi, 2008a. A novel fault tolerant reversible gate for nanotechnology based systems. Am. J. Applied Sci., 5: 519-523. DOI: 10.3844/ajassp.2008.519.523

- Haghparast, M. and K. Navi, 2008b. A novel reversible

BCD adder for nanotechnology based systems. Am.

J. Applied Sci., 5: 282-288. DOI: 10.3844/ajassp.2008.282.288

- Islam, M.S. and Z. Begum, 2008. Reversible logic synthesis of fault tolerant carry skip BCD adder. Bangladesh Aca. Sci. J., 32: 193-200. DOI: 10.3329/jbas.v32i2.2431

- Islam, M.S., M.M. Rahman, Z. Begum and M.Z. Hafiz, 2009. Fault tolerant reversible logic synthesis: Carry look-ahead and carry-skip adders. Proceedings of the International Conference on Advances Computational Tools for Engineering Applications, Jul. 15-17, IEEE Xplore Press, Zouk Mosbeh, pp: 396-401. DOI: 10.1109/ACTEA.2009.5227871

- Lala, P.K., J.P. Parkerson and P. Chakraborty, 2010. Adder designs using reversible logic gates. WSEAS Trans. Circ. Syst., 9: 369-378.

- Landauer, R., 1961. Irreversibility and heat generation in the computing process. IBM J. Res. Dev., 5: 183-191. DOI: 10.1147/rd.53.0183

- Peres, A., 1985. Reversible logic and quantum computers. Phys. Rev., 32: 3266-3276. DOI: 10.1103/PhysRevA.32.3266

- Thapliyal, H., S. Kotiyal and M.B. Srinivas, 2006. Novel BCD adders and their reversible logic implementation for IEEE 754r format. VLSI Design India, pp: 387-392.

- Toffoli, T., 1980. Reversible computing. Automata, Languages Programm., 85: 632-644. DOI: 10.1007/3-540-10003-2\_104