American Journal of Applied Sciences 7 (10): 1353-1357, 2010 ISSN 1546-9239 © 2010 Science Publications

# Design of Capacitance to Voltage Converter for Capacitive Sensor Transducer

A.H.M. Zahirul Alam, Nurul Arfah, Sheroz Khan and Md. Rafiqul Islam Department of Electrical and Computer Engineering, Faculty of Engineering, International Islamic University Malaysia, Kuala Lumpur, Malaysia

Abstract: Problem statement: The design of Capacitance to Voltage Converter (CVC) for capacitive sensor transducer was presented. The proposed design will reduce the size, power consumption and supply voltage of the circuit and can be used in high frequency band transducer. Approach: The design was implemented using the Operational amplifier (Op amp) and capacitive network. The circuit was simulated using the PSPICE model parameters based on standard 0.13  $\mu$ m CMOS process. Results: The design was able to measure a wide range of capacitance variations for the capacitive transducer. The performance analysis of the design showed desirable performance parameters in terms of response, low power consumption and a linear output voltage of 1.2 V was achieved. Conclusion/Recommendations: The output voltage of the circuit varied linearly with the variation of capacitive transducer capacitance variation. The improved converter was compact and robust for integration into capacitive measuring systems and suitable for use in environment that making use of higher frequency band.

Key words: Capacitance, converter, capacitive transducer, sensor transducer, telemetry, measuring systems

# INTRODUCTION

Sensor transducers are widely used in the instrument measurement systems such as in the biomedical, automotives, telecommunications, food industry, water treatment plants and chemistry industry. The sensor itself can be defined as a device that can measure (or detect) changes in physical stimulus parameter (such as acoustic pressure, electrical or magnetic field changes, optical, thermal and mechanical) and turns the detected change or measured stimulus parameter signal into a recordable signal or pulse. On the other hand transducers are devices that convert a form of an input energy into a same or another form of output energy. There are many research has been done on the sensor transducers using the capacitance to frequency conversion for the past few years. The sensor transducer is suitably used for pressure variations (Takahata converting and Gianchandani. 2008), humidity measurements (DeHennis and Wise, 2005) into corresponding signal with equivalent frequency. Further, such transducers have been used in water level measurement system or even telemetry systems (Mariun et al., 2006; Reverter et al., 2007).

Various methods have been reported (Lotters et al., 1999; Alia, 2007; Zahirul Alam et al., 2009; Ghafar-Zadeh et al., 2009; Arfah et al., 2010; Chatzandroulis et al., 2000) to deal with capacitance to voltage conversion. Some of them, for instance the method utilizing ratioarm bridge is symmetrical and sensitive, but it has the disadvantage that transformer coils have to be used which is difficult to implement monolithically. Others, for example the modified Martin oscillator with microcontroller is not capable of handling capacitance changes with frequencies higher than 10 Hz. Another approach is based on charge integration (Lotters et al., 1999). It is less susceptible to parasitic; however, a fairly large feedback resistor is usually needed to bias the sensing electrode. In the past, the large resistor can be implemented either by sub-threshold transistors or long transistors in triode region (Geen et al., 2002). However, values of such MOS (Maiti and Maiti, 2010) resistors depend on the terminal voltages which are difficult to control. For pressure sensor applications, since the capacitance and output voltage of the CVC change over a wide range, the linearity of the feedback resistor degrades seriously. Besides, a large transistor will introduce parasitic capacitance which would cause signal attenuation in a capacitive sensing front-end.

Corresponding Author: A.H.M. Zahirul Alam, Department of Electrical and Computer Engineering, Faculty of Engineering, International Islamic University Malaysia, Kuala Lumpur, Malaysia

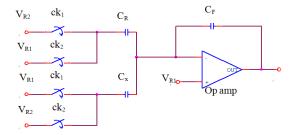

Fig. 1: Capacitance to Voltage Converter (CVC)

In this study the capacitance to voltage converter circuit is designed based on third generation Berkeley Short-channel Insulated Gate FET (IGFET) Model 3 (BSIM3) version 3.2 of 0.13 µm technology and performance of the design is presented.

Proposed ADC architecture: The Capacitance to Voltage Converter (CVC) circuit is designed by using the Operational amplifier (Op amp) by considering the offset voltage of the Op amp and the charge injection error of a switch. The schematic diagram of the CVC circuit is shown in Fig. 1.  $C_x$  is the capacitor of the detected sensor and  $C_R$  and  $C_F$  are the designed capacitors.  $V_{R1}$  is the common-mode voltage and  $V_{R2}$  is the reference voltage. The signals ck1 and ck2 are two non overlapping phase clocks. When the signal ck<sub>2</sub> is logic high, the voltage  $V_{R2}$  will charge the capacitor  $C_x$ , whereas the capacitor  $C_F$  stores the offset voltage of the Op amp. When the signal  $ck_1$  is logic high, the capacitor  $C_F$  is connected to the output. The voltage  $V_{R2}$ charges the capacitor C<sub>R</sub>. Thus, by following the principle of charge conservation, the output voltage  $V_0$ will be derived as follows:

$$C_{x}(V_{R2} - V_{R1} - V_{os}) + C_{R}(0 - V_{os}) + C_{F}(0 - V_{os}) = C_{x}(0 - V_{os}) + C_{R}(V_{R2} - V_{R1} - V_{os}) + C_{F}(V_{o} - V_{os})$$

(1)

Therefore:

$$V_{o} = \frac{C_{x} - C_{R}}{C_{F}} (V_{R2} - V_{R1})$$

(2)

where,  $V_{os}$  is the offset voltage of the Op amp and the output voltage is free from Op amp offset as observed in Eq. 2.

#### MATERIALS AND METHODS

The Op amp plays an important role in designing the converter. Therefore the Op amp is designed based on 0.13  $\mu$ m CMOS technology.

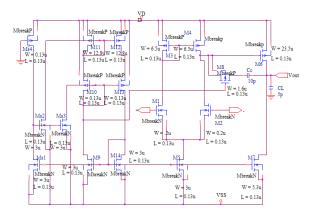

Fig. 2: Schematic for Op amp

The schematic diagram of the Op amp is shown in Fig. 2. The circuit consists of start-up, bias and two-stage Op amp. The Op amp gain is derived as:

$$C_{x}(V_{R2} - V_{R1}) = C_{x}(V_{R1} - OP_{-}) + C_{R}(V_{R2} - OP_{-}) + C_{F}(V_{o} - OP_{-})$$

(3)

$$V_{R1} - OP_{-} = \frac{V_0}{A}, \qquad A: \text{ Gain}$$

(4)

Therefore:

$$V_{o} = \frac{C_{x} - C_{R}}{C_{F}} (V_{R2} - V_{R1}) \times \left( \frac{1}{1 + \frac{1}{A} \left( \frac{C_{F} + C_{R} + C_{x}}{C_{F}} \right)} \right)$$

$$= \frac{C_{x} - C_{R}}{C_{F}} (V_{R2} - V_{R1}) \times \left( 1 - \frac{1}{A \left( \frac{C_{F}}{C_{F} + C_{R} + C} \right)} \right)$$

(5)

It is observed from Eq. 5 that the gain of Op amp should be high so that the output voltage  $V_0$  is insensitive of the Op amp gain as mentioned in Eq. 2. The unity gain bandwidth and phase margin of the Op amp need to be considered for stable response and frequency range of operation.

The proposed CVC circuit has been simulated using the model parameters of a standard 0.13  $\mu$ m CMOS process. The width for the CMOS devices are chosen based on designed equations (Allen and Holberg, 2002; Ali and Khamis, 2005; Nabhan and Abdallah, 2010). The supply voltage of the Op amp is chosen ±1.2V for reducing power consumption.

### **RESULTS AND DISCUSSION**

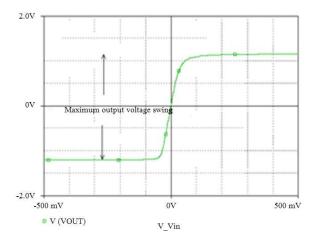

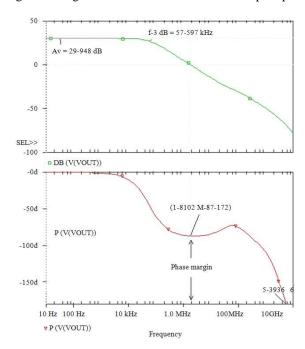

The voltage transfer a characteristic of the Op amp is shown in Fig. 3. Figure 4 shows the frequency response of the Op amp. The bandwidth gain is approximately 1.8 MHz.

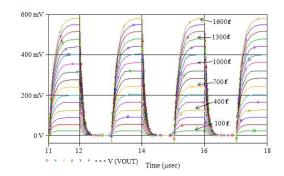

The detection capacitance  $C_X$  is varied from 20-1700 fF with the increment of 20 fF. Capacitance  $C_R$ and  $C_F$  are set to 1 and 1500 fF respectively for this capacitance range. The output voltage waveform with the variation of capacitance,  $C_X$  of the circuit is shown in Fig. 5.

Fig. 3: Voltage transfer characteristics of the Op amp

Fig. 4: Gain and phase of the Op amp

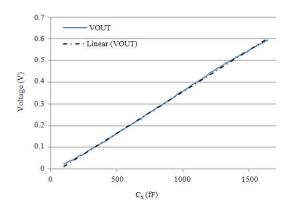

The peak output voltage from the Fig. 5 is plotted in Fig. 6 with the variation of  $C_x$ . The Fig. 6 shows that the output voltage varies linearly with the variation of  $C_x$ .

The operational amplifier differential gain, Ad = 29.948 dB or 31.43 V/V and the 3-dB frequency,  $f_{.3}dB = 57.597$  kHz. Thus, this value of A<sub>d</sub> is close to the estimated using the large signal differential transfer characteristic. The phase margin is 92.8° which is more than 60° for stable operation without ringing. The overall performance of the Op amp is tabulated in Table 1.

Fig. 5: Output voltage wave form of the converter circuit with the variation of  $C_x$

Fig. 6: Peak output voltage with the variation of  $C_x$

Table 1: Performance for Op amp

| Specification                         | Simulation using P spice    |

|---------------------------------------|-----------------------------|

| Differential gain, A <sub>d</sub>     | 31.43 V/V                   |

| Offset voltage, V <sub>os</sub>       | 884 μV                      |

| Output dc offset, Vout                | 0.0279 V                    |

| V <sub>out</sub> swing range          | -1V-470 mV                  |

| Open-loop gain, Av                    | 31.434 V/V                  |

| Open-loop gain, Av                    | 29.948 dB                   |

| Unity gain bandwidth, GB              | 1.8 MHz                     |

| Power dissipations, P <sub>diss</sub> | 0.939 mW                    |

| Phase margin, PM                      | 92.8°                       |

| ICMR                                  | -0.23-1.0 V                 |

| 3-dB frequency, f <sub>H</sub>        | 57.597 kHz                  |

| Slew rate, SR                         | 14 and -19 V $\mu sec^{-1}$ |

| Power supply                          | ± 1.2 V                     |

It is noted that the CVC circuit can be used up to 58 kHz.

The value of capacitive transducer,  $C_x$  is chosen from 20-1700fF, then any changes of capacitance of the capacitive transducer results linear output voltage within the range of 0.02-0.59V for the variation of the capacitance from 100-1640fF, respectively. The output voltage can be obtained by using following equation:

$$V_{o} = -0.017 + 3.70 \times 10^{-4} C_{X} \ 100 \text{fF} \le C_{X} \le 1640 \text{fF}$$

(6)

where,  $C_x$  in fF and  $V_o$  in Volts. It is note that the Eq. 6 is valid for the circuit with  $C_R = 1$  fF and  $C_F = 1500$  fF. However, by changing the value of  $C_R$  and  $C_F$ , other ranges of capacitive transducer can be used. If order to design a circuit that can be detect capacitive transducer capacitance changes within pF range then  $C_R$  and  $C_F$  are to be chosen in pF range with appropriate ratio.

# CONCLUSION

A capacitance measuring systems for sensor transducer was designed in this study is suitable for low voltage applications for less than  $\pm 1.2$  V. It is observed that the output voltage is linearly varies with the variation of capacitive transducer capacitance within a wide range. Based on these advantages, it is also suitable to be implemented in the pressure, humidity and other sensors applications since it changes over a wide range. The circuit is implementing a short channel technology device that will not only reduce the parasitic capacitance introduced by the transistors but also will benefit to high speed system sensing implementing in lower scale device. The improved converter is compact and robust for integration into capacitive measuring systems and suitable for use in environment that making use of higher frequency band.

### ACKNOWLEDGMENT

This study is funded by the Research Management Center, International Islamic University Malaysia through Endowment fund.

#### REFERENCES

Ali, M.L. and N.H. Khamis, 2005. Design of a current sensor for IDDQ testing of CMOS IC. Am. J. Applied Sci., 2: 682-687. http://www.scipub.org/fulltext/ajas/ajas23682-687.pdf

- Alia, M.A.K., 2007. Custom design of an analogue input digital output interface card for small Size PLCs. Am. J. Applied Sci., 4: 479-483. http://www.scipub.org/fulltext/ajas/ajas47479-483.pdf

- Allen, P.E. and D.R. Holberg, 2002. CMOS Analog Circuit Design. 2nd Edn., Oxford University Press, New York, USA., ISBN: 0195116445, pp: 250.

- Arfah, N., A.H.M. Zahirul Alam and S. Khan, 2010. Design of capacitive measuring systems for high frequency band sensor transducer. Proceeding of the International Conference on Computer and Communication Engineering, May 11-12, IEEE Xplore Press, Kuala Lumpur, pp: 1-4. DOI: 10.1109/ICCCE.2010.5556850

- Chatzandroulis, S., D. Tsoukalas and P.A. Neukomm, 2000. A miniature pressure system with a capacitive sensor and a passive telemetry link for use in implantable applications. J. Microelectromech. Syst., 9: 18-23. DOI: 10.1109/84.825772

- DeHennis, A.D. and K.D. Wise, 2005. A wireless microsystem for the remote sensing of pressure, temperature and relative humidity. J. Microelectromech. Syst., 14: 12-22. DOI: 10.1109/JMEMS.2004.839650

- Geen, J.A., S.J. Sherman, J.F. Chang and S.R. Lewis, 2002. Single-chip surface micromachined integrated gyroscope with 50°/h Allan deviation. IEEE J. Solid-State Circ., 37: 1860-1866. DOI: 10.1109/JSSC.2002.804345

- Ghafar-Zadeh, E., M. Sawan and D. Therriault, 2009.

CMOS based capacitive sensor laboratory-on-chip: A multidisciplinary approach. Analog Integr. Circ.

Sign. Process., 59: 1-12. DOI: 10.1007/s10470-008-9239-9

- Lotters, J.C., W. Olthuis, P.H. Veltink and P. Bergveld, 1999. A sensitive differential capacitance to voltage converter for sensor applications. IEEE Trans. Instr. Measure., 48: 89-96. DOI: 10.1109/19.755066

- Mariun, N., D. Ismail, K. Anayet, N. Khan and M. Amran, 2006. Simulation, design and construction of high voltage DC power supply at 15 kV output using voltage multiplier circuits. Am. J. Applied Sci., 3: 2178-2183. DOI: 10.3844/ajassp.2006.2178.2183

- Maiti T.K. and C.K. Maiti, 2010. DFM of strainedengineered MOSFETs Using technology CAD. Am. J. Eng. Applied Sci., 3: 683-692. DOI: 10.3844/ajeassp.2010.683.692

- Nabhan I. and M. Abdallah, 2010. A novel low-power CMOS operational amplifier with high slew rate and high common-mode rejection ratio. Am. J. Eng. Applied Sci., 3: 189-192. DOI: 10.3844/ajeassp.2010.189.192

- Reverter, F., X. Li and G.C.M. Meijerb, 2007. Liquidlevel measurement system based on a remote grounded capacitive sensor. Sensors Actuat. A: Phys., 138: 1-8. DOI: 10.1016/j.sna.2007.04.027

- Takahata, K. and Y.B. Gianchandani, 2008. A micromachined capacitive pressure sensor using a cavity-less structure with bulk-metal/elastomer layers and its wireless telemetry application. Sensors, 8: 2317-2330. http://www.eecs.umich.edu/~yogesh/pdfs/journalp ublications/MDPI%20Sensors\_Wireless%20Elasto mer%20Pressure%20Sensor%204-08.pdf

- Zahirul Alam, A.H.M., M.R. Islam, S. Khan and M.M. Rashid, 2009. Microelectrical mechanical systems switch for designing multi-band antenna. J. Comput. Sci., 5: 479-486. http://www.scipub.org/fulltext/jcs/jcs57479-486.pdf