American Journal of Applied Sciences 1(1): 26-32, 2004 ISSSN: 1546-9239 © Science Publications, 2004

# A Fully Integrated Dual-Band Low Noise Amplifier for IEEE 802.11 and Hiper LAN Application

<sup>1</sup>Mow Shouxian, <sup>2</sup>Ma Jianguo, <sup>3</sup>Yeo Kiat Seng and <sup>4</sup>Do Manh Anh Nanyang Technological University, Singapore Center for Integrated Circuits and Systems (S2.1-B3-01), School of EEE, NTU, Singapore,

**Abstract:** A fully-integrated dual-band Low Noise Amplifier (LNA), which can be used for IEEE 802.11 and Hiper LAN applications, was investigated in this paper. The proposed LAN was implemented entirely pm a single chip based on a standard 0.18  $\mu$ m 1P6M CMOS process. It draws 13 mA current from a 1.5-V voltage supply and achieves power gains of 17 and 10 dB, noise figure of 3.7 and 4.2 dB at 2.4 and 5.3 GHz respectively.

Key word: Low Noise Amplifier (LNA), Dual Band, IEEE 802.11 and HiperLAN

#### INTRODUCTION

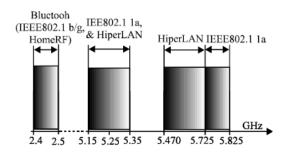

COMS technology is becoming to a suitable technology for implementing wireless portable communication for terminals due to the fact that the gate lengths of MOS devices have been scaled down to submicron regime. Furthermore, by incorporating its high integration level and low cost, COMS technology is a good candidate for RF/analogue/digital mixed signal application. At percent, there exist many communication standards due to the rapid growth of wireless service industry (e.g., Fig. 1). Therefore, a multi-standard COMS RF single chip solution for wireless communication system is expected to be realized. In practice, one of the key bottlenecks for developing single-chip multi-functional а communication device is to design a fully-integrated dual-band/multi-band Low Noise Amplifier (LNA) owing to the LAN's importance in the receiving path of current wireless communication systems. For this purpose, a fully integrated dual-band LAN which is able to provide simultaneous gains at two different frequency bands (2.4GHz-2.5GHz and 5.15GHz-5.35GHz), based on Chartered Semiconductor Manufacturing (CSM) 0.18µm CMOS technology, will be invested in this paper.

#### **Dual-band LAN designs:**

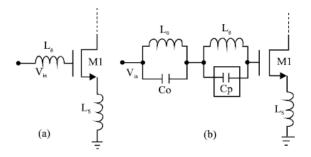

**Input stage matching:** LAN designers usually pay much attention to the input matching design, because the matching quality will greatly influence the overall performance of the designed LAN. Recent research shows that the optimal input stage topology, which has a small Noise Figure (NF) and a reasonable gain, is the source inductive degeneration input stage<sup>[1]</sup>, as shown in Fig. 2(a). Its input impedance can be expressed as:

$$Z_{in} = \left\{ \left[ \frac{g_{m1}}{C_{gs}} \right] L_s \right\} + \left\{ j\omega L_s + j\omega L_s + \frac{1}{j\omega C_{gs}} \right\}$$

(1)

Fig. 1: Communication standard distribution in the range of 2.4-6GHz

Fig. 2: Source inductive degeneration input stage (b) Modified dual-band input stage

To get a 50 $\Omega$ , whereas the imaginary part should zero the frequency be at of interest  $(\omega_{0=1}/\sqrt{(L_g + L_s)C_{gs})}$ . This is the design rule for single-band LAN, similar topology can be adopted. However, one must introduce another zero point (corresponding to  $\omega_{02}$ ) to the imaginary part, since the dual-band LAN has to operate in two different frequency bands (2.4GHz-2.5GHz and 5.15GHz-5.35GHz in this design). The zero point can be achieved by connecting an additional parallel  $L_0C_0$ network in series with the gate inductor  $L_{\sigma}^{[2,3]}$ . The corresponding input impedance is:

$$Z_{in} = \{ j\omega L_{s} + j\omega L_{s} + \frac{1}{j\omega C_{gs}} + \frac{j\omega L_{0}}{1 - \omega^{2} L_{0}C_{0}} \}$$

(2)

+  $\{ g_{ml} L_{s} / C_{gs} \}$

Unfortunately, in order to realize the series resonance with M1's gate to source capacitance C<sub>gs</sub> (about 0.23pF for a 240µm/0.18µm NMOS transistor) at a certain frequency, Lg has to be very large. Sometimes it is up to 10 nH<sup>[3]</sup>. It is known a large and high quality factor (Q) inductor is difficult to be implemented on chip with a standard CMOS process. Even if it was implemented, it consumes a large area (e.g., a radius of more than 125µm with CSM 0.18µm CMOS technology). Moreover, to ensure the normal operation of the on-chip inductor, the distance between the inductor and any other components should be at least 50 µm when drawing layout<sup>[4]</sup>. It means a 10nH inductor will occupy an area with a radius of at least 175 µm, which is very costly. Therefore, to reduce the cost, come modification is done with our work. A capacitor  $C_{\text{p}}$  is connected in parallel with  $L_{\text{g}},$  as depicted in Fig. 2(b). To this topology, input impendence can be derived as:

$$Z_{in} = \{j\omega L_s + \frac{j\omega L_{g2}}{1 - \omega^2 L_{g2}C_p} + \frac{1}{j\omega C_{gs}} + \frac{j\omega L_0}{1 - \omega^2 L_0 C_0}\} + \{g_{ml}L_s / C_{gs}\}$$

(3)

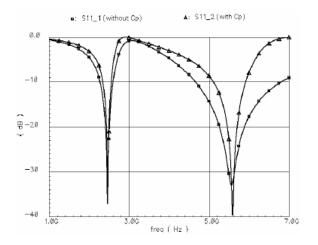

In contrast with (2), the effect of  $C_p$  (about  $1_pF$ , which occupies  $30\mu m \times 30\mu m$  area),  $L_g$  can be reduced to 2nd (65 $\mu$ m radius). Consequently, up to 56% chip area is saved, as summarized in Table 1. Fig. 3 compares the input reflection coefficients  $S_{11_2}$  and  $S_{11_2}$  under the conditions without  $C_p$  ( $L_g = 10nH$ ,  $C_p = 0$ ) and with  $C_p$  ( $L_g = 2nd$ ,  $C_p = 1pF$ ). The pot indicates  $S_{11_2}$  does not degrade at the required frequency bands and proves the availability of the above mentioned area-reducing method.

# Noise figure optimization:

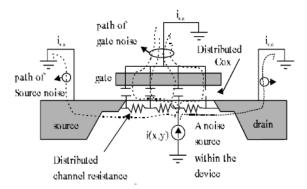

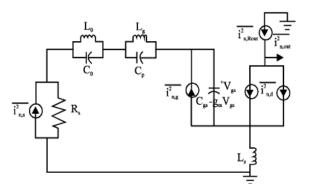

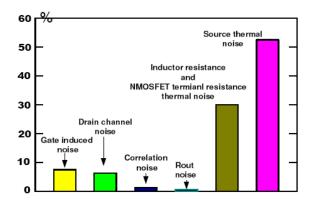

Noise sources: a small NF is another common consideration in LNA designs, in a MOS device, the dominant channel noise sources are drain noise  $\bar{i}_{n,d}^2 = 4kT\gamma g_{d0}\Delta f$ gate induced and noise  $\overline{i_{n,d}^2} = 4kT\delta g_g \Delta f^{[5-8]}$ . Other prominent noise sources are gate parasitic resistance thermal noise  $i_{n,R_{o}}^{2}$  substrate thermal noise  $i_{n,Sub}^2$  and  $i_{n,corr}^2$ , which is due to the correlation of  $i_{n,g}^2$  and  $i_{n,d}^2$ . Fig. 4 gives a visual illustration and Fig. 5 depicts an equivalent circuit with noise sources of the proposed dual-band LNA.

Table 1: Comparison of Lg1 and Lg2

| Tuble 1. Companison of L                  | Egi and Eg2      |                    |

|-------------------------------------------|------------------|--------------------|

|                                           | Lg1 (without Cp) | Lg2 (Cp connected) |

| Inductance (nH)                           | 10               | 2                  |

| Radius including the                      | 50               |                    |

| µm outside the inductor                   | 175µm            | 115µm              |

| Area (mm <sup>2</sup> )                   | 0.0962           | 0.0415             |

| Area of C <sup>p</sup> (mm <sup>2</sup> ) | 0                | 0.0009             |

| Sum (mm <sup>2</sup> )                    | 0.0962           | 0.0424             |

| Saved area (%)                            | 0                | 56                 |

Fig. 3: Comparison of  $S_{11}$  @  $L_{g1} = 10nH$ ,  $C_p = 0$  and  $L_{g2} = 2nH$ ,  $C_p = 1pH$

Fig. 4: Description of various noise sources in a MOS transistor<sup>[5]</sup>

Fig. 5: Small signal equivalent circuit with noise sources of the proposed dual-band LNA

**Output noise:** According to Fig. 5, through circuit analysis, the transfer function of the various noise sources can be achieved. Then the corresponding output noise is expressed as follows:

$$\overline{i_{n,0,Rs}^{2}} = \left| \frac{g_{m}R_{s}}{j2\omega_{0}C_{gs}R_{s} + j\omega C_{gsD_{0}}} \right|^{2} \overline{i^{2}}_{n,Rs}$$

(4)

$$\overline{i_{n,o,d}^2} = \frac{1}{4} \overline{i_{n,d}^2}$$

(5)

$$\overline{i_{n,o,g}^{2}} = \begin{vmatrix} \frac{g_{m}}{j2\omega_{0}C_{gs}} \\ (1 - \frac{1}{j\omega_{0}C_{gs}R_{s} + j\omega C_{gs}D_{0}}) \end{vmatrix}^{2} \overline{i_{n,g}^{2}}$$

(6)

$$\overline{i_{n,o,R_{out}}^2} = \overline{i_{n,R_{out}}^2}$$

(7)

$$\overline{i_{n,o,corr}^{2}} = \frac{g_{m}|c|}{2\omega_{0}C_{gs}}$$

$$(1 - \frac{j\omega C_{gs}D_{0}}{(j\omega C_{gs})^{2}D_{0}^{2} + \omega^{2}C_{gs}^{2}R_{s}^{2}})\sqrt{i_{n,g}^{2}.\overline{i_{n,d}^{2}}}$$

(8)

Is the imaginary part of the input impedance (see (3)) and equal to zero at the two corresponding resonant frequencies (2.45GHz and 5.3GHz in this paper). In terms of the above equations, the noise factor noise can be obtained:

$$F = \frac{\overline{i_{n,0,Rs}^{2} + \overline{i_{n,0,g}^{2} + \overline{i_{n,0,d}^{2} + \overline{i_{n,0,corr}^{2} + \overline{i_{n,0,R_{out}}^{2}}}}}{= 1 + \frac{\delta\alpha}{5g_{m}R_{s}} \{ (j\omega C_{gs} D_{0} - 1)^{2} + \omega^{2} C_{gs}^{2} R_{s}^{2} \}$$

$$+ \frac{\gamma}{\alpha g_{m}R_{s}} \{ (j\omega C_{gs} D_{0})^{2} + \omega^{2} C_{gs}^{2} R_{s}^{3} + \frac{2|c|}{g_{m}R_{s}}$$

$$\sqrt{\frac{\gamma\delta}{5}} \{ (j\omega C_{gs} D_{0} + \omega^{2} C_{gs}^{2} R_{s}^{2} \}$$

(9)

The noise factor at resonance frequency  $\omega_0$  (D<sub>0</sub> = 0 under this condition) can be achieved as well:

$$F_{0} = 1 + \frac{\delta\alpha}{5g_{m}R_{s}} \{1 + \omega_{0}^{2}C_{gs}^{2}R_{s}^{2}\} \frac{\gamma}{\alpha g_{m}R_{s}} + \omega_{0}^{2}C_{gs}^{2}R_{s}^{2} + \frac{2|c|}{g_{m}R_{s}}\sqrt{\frac{\gamma\delta}{5}}\omega_{0}^{2}C_{gs}^{2}R_{s}^{2}$$

(10)

**Noise optimization:** In CMOS LNAs the MOS transistor usually operates in saturation region<sup>[6]</sup>, a simplified equation for the drain current  $I_{ds}$  when the transistor operates in saturation is<sup>[7]</sup>:

$$I_{ds} = \frac{W}{2\xi L_{eff}} \mu_{eff} C_{o\chi} (V_{GS} - V_T)^2$$

(11)

where,  $\mu_{eff}$  is the carrier effective mobility in the transistor channel and  $\xi$  is a factor, which takes the short channel effect and other effect into account and is often set to one in the simplified MOS transistor model, but can be significantly larger in short channel MOS transistors. Taking the derivative of (11) with respect to  $V_{GS}$  yields:

$$g_{m} = \frac{W}{\xi L_{eff}} \mu_{eff} C_{o\chi} (V_{GS} - V_{T}) = \sqrt{\frac{2W}{\xi L_{eff}}} \mu_{eff} C_{o\chi} I_{ds}$$

(12)

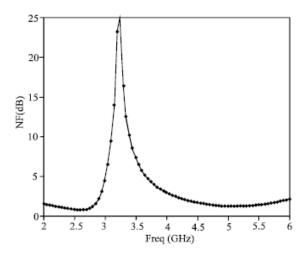

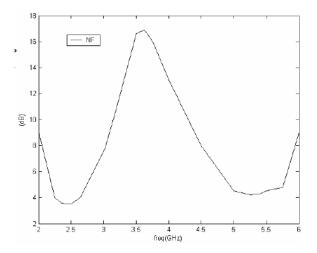

Combining (9), (12),  $C_{gs} \approx \frac{2}{3} WLC_{o\chi}$ <sup>[7, 8]</sup> and other parameters, the relationship of NF versus frequency can be plotted, shown in Fig. 6.

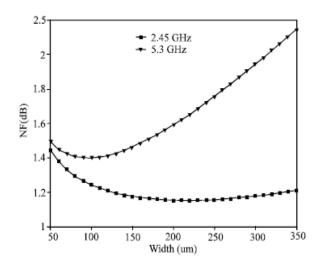

In practice, we are more interested in the NF at the resonant frequencies such as 2.45GHz and 5.3GHz. According to the expressions of  $g^m$  and  $C_{gs}$ , (10) can be rewritten as:

$$F_0 = 1 + \frac{R_G}{R_s} + b_1 W^{-1/2} + b_2 \omega_0^2 L_{eff}^2 W^{3/2}$$

(13)

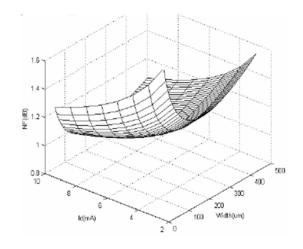

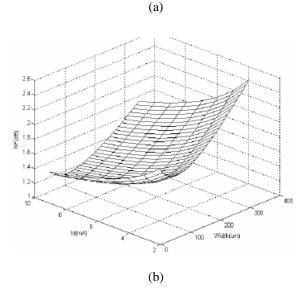

where,  $b_1$  and  $b_2$  are equation coefficients. In terms of (13), group of plots is presented. Fig. 7 gives a plot of NF versus transistor width (W) at frequencies 2.45GHz and 5.3GHz respectively; Fig. 8(a) and (b) depicts the relationship among NF, W and the drain current I<sub>ds</sub>, which is corresponding to the LAN's power consumption  $P_d = V_{dd} I_{ds}$ . It can be found that (13) contains terms which are constant, proportional to W. Therefore, there must corresponding to the minimum noise factor. Different (13) with respect to W and equate it to zero yields.

$$W_{opt} = \sqrt{\frac{b_1}{3b_2\omega_0^2 L_{eff}^2}}$$

(14)

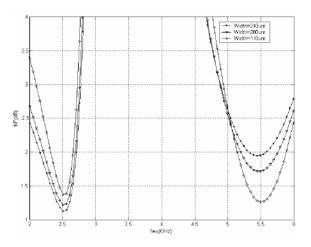

For a fixed current  $I_{ds} = 8$ mA, (14) generates two  $W_{opt}$  values of  $W_{opt1} = 240\mu$ m and  $W_{opt2} = 110 \ \mu$ m corresponding to  $f_{01} = 2.45$  GHz and  $f_{01}$  5.3 GHz respectively. Hence a tradeoff between  $W_{opt1}$  and  $W_{opt2}$  has to be made. A transistor width of 200  $\mu$ m is finally chosen after consideration of various factors, such as the gain and NF as well as the circuit stability. Fig.9 compares the NF with different W of 240  $\mu$ m, 110  $\mu$ m and 200  $\mu$ m. Following the above procedure and plots, one can optimize the LNA according to different design requirements.

Fig. 6: NF vs. Freq, for W/L =240 $\mu$ m/0.18 $\mu$ m,  $\gamma$  =1.8,  $\delta$  =3,  $\xi$ =1.6,  $\alpha$  =0.8,  $\mu_{eff}$ =0.035m<sup>2</sup>/V,

Fig. 7: NF vs. W for  $\gamma$  =1.8,  $\delta$  =3,  $\xi$ =1. 6,  $\alpha$  =0. 8,  $\mu_{eff}$  =0. 035  $m^2/V,$   $C_{ox}$  0. 008 F/m² and  $I_{ds}$  = 8mA

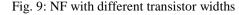

LNA implementation and measurement results: Based on the above analysis, a concurrent dual-band LNA is designed. Figure 10 is the simplified schematic diagram. It is a two-stage amplifier with an additional buffer stage for output matching purposes. In the LNA, cascade structure is used to reduce the influence of the influence of the gate-to-drain overlap capacitance  $V_{gd}$ on LNA's input impendence and to improve the LNA's reverse isolation to prevent the Local Oscillator (LO) feed through from the subsequent mixer back to the LNA's RF input. In the circuit, the dimension of the M2 is the same as M1; whereas M3 and M4 have the same dimension of  $150\mu$ m/0.18 $\mu$ m. The selection of L<sub>1</sub> and L<sub>2</sub> is based on the resonant frequency and quality factor for a certain power gain. Capacitor Ce is a Qenhancement capacitor<sup>[9]</sup>.

Fig. 8: NF vs. W and  $I_{ds}$  for (a)  $f_{01} = 2.45$ GHz and (b)  $f_{02} = 5.3$ GHz

Fig. 10: Simplified schematic diagram of the dual-band LNA

Fig. 11: Measured S-parameters of the dual-band LNA

| Table 2: detailed | performance of the dual-band LNA |

|-------------------|----------------------------------|

|-------------------|----------------------------------|

|                      | 1st band | 2nd band |  |

|----------------------|----------|----------|--|

| $V_{dd}(V)$          | 1.5      |          |  |

| $P_{d}(mW)$          | 21       |          |  |

| Operating band (GHz) | 2.4-2.5  | 5.15-5.4 |  |

| $S_{11}(dB)$         | -128     | -2520    |  |

| S <sub>22</sub> (dB) | -2018    | -87      |  |

| S <sub>12</sub> (dB) | -35 -    | -16      |  |

| NF (dB)              | 3.7      | 4.2      |  |

Fig. 12: Measured noise figure

Fig. 13: Die photo of the dual-band LNA (0.8mm×0.85mm)

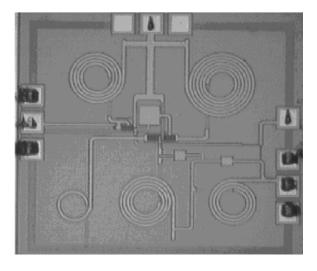

Properly adjusting the parameters of the passive and active components of the schematic can make the LNA work at two different frequency bands at the same time, which is meaningful for the development of multistandard operation devices. The proposed dual-band LNA was fabricated at CSM and was measured using a HP8510C network analyzer with on-wafer RF probes. Fig. 11 and 12 demonstrate the measured S-parameters and noise figure. It is shown that the LNA has a power gain of about 17dB at the first band and a gain of 8-10dB at the second band. Detailed performance can be found in Table 2. Fig. 13 is the die photo of the proposed dual-band LNA.

# DISCUSSION

The parasitic resistance of the on-chip inductors: The measurement data indicate that the LNA's noise figure is not as good as GaAs devised.

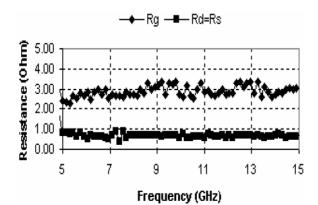

Fig. 14: Parasitic resistance of several on-chip inductors based on a standard CMOS process

Fig. 15:  $\gamma$  versus V<sub>GS</sub> characteristics of n MOSFET<sup>[10]</sup>

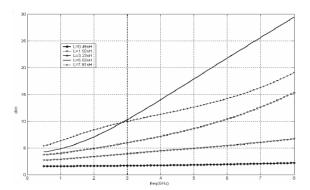

This is mainly due to the loss on-chip integrated inductors in a standard CMOS technology. In practice, the parasitic resistance of the low-Q inductors has a severe impact on the LNA's noise performance. Figure 14 presents the parasitic resistance  $R_p$  versus frequency of several on-chip inductors based on CSM 0.18 µm CMOS process. The figure shows that R<sub>p</sub> increases with frequency. For a 1.92nH inductor, its  $R_p$  is about 5 $\Omega$  at 5.3GHz; whereas for a 7.81nH inductor, the 50 $\Omega$  single source resistance R<sub>s</sub>. Therefore, when designing and LNA, one should avoid using large inductance inductors, since their RP is relative larger compared to the smaller ones. Additionally, the parasitic resistance of the on-chip inductors must be taken into account when doing noise optimization for a more accurate noise figure prediction. Generally, the total  $R_p$  of all the on-chip inductors of an LNA's overall figure degradation, R<sub>p</sub> can reduce the LNS's gain as well.

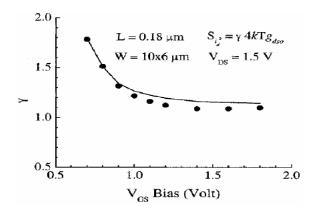

**Channel noise coefficienty:** channel noise coefficient  $\gamma$  is a bias-dependant factor, for long channel devices, it is between 1 (in the linear region with  $V_{ds} = 0$ ) and 2/3 in saturation<sup>[8]</sup>. For short channel devices  $\gamma$  is much greater due to short channel effects such as channel-length modulation and velocity saturation. There does not exist a constant value for  $\gamma$  for short channel devices. In the past few years, the value between 1-6 has been used. In terms of Fig. 15.

Fig. 16: Terminal resistance of nMOS with  $L = 0.8 \mu m$ , W = 8 $\mu m$  and n<sub>f</sub> = 25

Fig. 17: Noise contribution of different noise sources in a CMOS LNA

**Terminal resistance of MOSFET:** the gate resistance  $R_g$ , source resistance  $R_s$  and drain resistance  $R_d$  can contribute thermal noise to the total circuit as well. Fig. 16 illustrates the terminal resistance versus frequency for a transistor size of 200µm/0.18µm. It can be found that the total terminal resistance of the n MOSFET is about 5 $\Omega$ , which provides about 5% noise contribution.

We finally summarize the noise contribution of the various noise sources in a fully-integrated CMOS LNA as shown in Fig. 17. The statistic figure indicates the obstacle for RF circuit designs. How to achieve high-Q, low cost on-chip passive components are an urgent problem to be solved.

# CONCLUSION

A CMOS dual-band low noise amplifier has been investigated in this paper. The LNA has two investigated in this paper. The LNA has two pass bands and can be used for Bluetooth, wireless LNA and Hiper LNA applications. The LNA is implemented entirely on a single-chip and is possible to be integrated with other CMOS devices. In this paper, a method to reduce the gate inductor as well as a procedure for dual-band LNA noise optimization is also presented. The design of the proposed LNA indicates with the ever-continuing downscaling of CMOS technologies, a fully-integrated multi-standard operation wireless communication system implemented using a low cost CMOS process becomes possible.

## REFERENCES

- 1. Andreani, P. And H. Sjolland, 2001. The noise optimization of an inductively degenerated CMOS low noise amplifier, IEEE transactions on circuits and Systems-II: analog and digital signal processing. 48: 835-841.

- 2. Hashemi, H. And A. Hajimiri, 2002. Concurrent multiband low-noise amplifiers: theory, design and applications, IEEE Trans MTT., 50: 288-301.

- Shouxian, M., M. Jianguo, Y. Kiat Seng and D. Manh Anh, 2002. A CMOS low noise amplifier for 802.11/Hiper LAn and wireless LAN applications for it. Symp. Cons. Elec., F-1-4.

- Chartered Semiconductor Manufacturing, 2001. CMS 0.18µm CMOS process design manual.

- 5. Tajinder Manku, 2001. Radio frequency CMOS, ISIC2001 tutorial material, Singapore.

- Shaeffer, D.K. and L. Thomas, 1997. A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE J. Solidstate Circuits, 32: 745-759.

- 7. Tsividis, Y.P., 1999. Operation and modelling of the MOS transistor 2nd Edn., McGraw-Hill: NY.

- 8. Van der Ziel, A., 1986. Noise in solid state devices and circuits. Wiley press: NY.

- Chan, K.L., M.A. Do, K.S. Yeo and J.G. Ma, 2000.

1.5 V 1.8 GHz bandpass amplifier. IEE Proceedings of Circuits Devices Systems, 147: 331-333.

- Chih-Hung Chen and M. Jamal Deen, 2002. Channel noise modelling of deep sublmicrom MOSFETs. IEEE Transactions on Electron Devices. 49: 1484-1487.