American Journal of Applied Sciences 8 (11): 1176-1181, 2011 ISSN 1546-9239 © 2011 Science Publications

## Single Core Hardware Module to Implement Boolean Function Classification Techniques

<sup>1</sup>Mohd. Marufuzzaman, <sup>2</sup>Md. Mamun, <sup>1</sup>Fazidah Hanim Hashim, <sup>1</sup>Labonnah F. Rahman <sup>1</sup>Department of Electrical, Electronic and Systems Engineering, <sup>2</sup>Smart Enginering System Research Group, Faculty of Engineering and Built Environment Universiti Kebangsaan Malaysia, 43600, Bangi, Selangor, Malaysia

**Abstract: Problem statement:** Boolean function classification plays an important role in the field like technology mapping for digital circuit design, function mapping for minimization and the development of universal logic modules. **Approach:** In this study, we present a single core hardware module to implement Boolean function classification techniques on Altera FLEX10K FPGA device for lossless data compression. The compression algorithm was performed by incorporating Boolean function classification into Huffman coding. This allows compression that was more efficient because the data had been categorized and simplified before the encoding was done. Simulation, timing analysis and circuit synthesis were commenced to verify the functionality and performance of the designated circuits which supports the practicality, advantages and effectiveness of the proposed single core hardware implementation. **Results:** The result shows a higher compression ratio. The average compression ratio was 25-37.5% from numerous testing with various text inputs with a maximum clock frequency of 27.9 MHz. **Conclusion:** The hardware implementation demonstrated complete, correct functionality and met all the initial system requirements.

Key words: FPGA, Boolean function, VHDL, Hardware implementation

## **INTRODUCTION**

The term Data Compression refers to the process of reducing the amount of the required data representing a given quantity of information. Data compression is increasingly more and more important in the development of computer and data communications technology. Various data compression technologies have been developed since the past few decades, using different algorithms for different applications. Some of the data compression techniques are Null Suppression, Run-Length Encoding, Huffman coding, Arithmetic coding, Lempel-Ziv-Welch coding, Discrete Cosine Transform, Joint Photographic Expert Group and Boolean Compression algorithm (Visweswariah et al., 2000). Boolean function classification technique has been traditionally designed for digital circuit applications. The main feature of this technique is because the functions belonging to some classes may be implemented more efficiently than the general sum of product implementation. Boolean function classification plays an important role in the field like technology mapping for digital circuit design, function

mapping for minimization and the development of universal logic modules (Chang and Falkowski, 1996).

The Field-Programmable Gate Arrays (FPGA) offers a potential alternative to speed up the hardware realization (Coussy et al., 2009; Marufuzzaman et al., 2010; Reaz et al., 2007; Reaz et al., 2011a). From the perspective of computer-aided design, FPGA comes with the merits of lower cost, higher density and shorter design cycle (Choong et al., 2005; Akter et al., 2008; Reaz et al., 2011b). It comprises a wide variety of building blocks. Each block consists of programmable look-up table and storage registers. where interconnections among these blocks are programmed through the hardware description language (Reaz et al., 2003; Amin et al., 2011). This programmability and simplicity of FPGA made it favorable for prototyping digital system. FPGA allows the users easily and inexpensively realize their own logic networks in hardware. FPGA also allows modifying the algorithm easily and the design period for the hardware becomes shorter by using FPGA (Choong et al., 2006; Mohd-Yasin et al., 2004).

Corresponding author: Mohd. Marufuzzaman, Department of Electrical, Electronic and Systems Engineering, Universiti Kebangsaan Malaysia, 43600, Bangi, Selangor, Malaysia

Tel: +603-89216316, Fax: +603-89216146

1176

In this studsy, we proposed the framework of FPGA-based hardware realization of Boolean compression algorithm by incorporating Boolean function classification into Huffman encoding (Tsai and Sadowska, 1997). By performing the Boolean function classification, the binary data is grouped into their classes through Huffman encoding, and the compression is done in a more efficient way because the data has been categorized and simplified before the encoding is done. The result has higher compression ratio. We had studied the existing Boolean classification schemes that are suitable for using in data compression. We also studied the new and alternative classification schemes that can be implemented in the algorithm. After finalizing the algorithm, the VHDL is selected as the hardware description language to realize the scheme. The use of VHDL for modeling is especially appealing since it provides a formal description of the system and allows the use of specific description styles to cover the different abstraction levels (architectural, register transfer and logic level) employed in the design (Reaz et al., 2005; 2006). In the computation of method, the problem is first divided into small pieces; each can be seen as a submodule in VHDL. Following the software verification of each submodule, the synthesis is then activated. It performs the translations of hardware description language code into an equivalent netlist of digital cells. The synthesis helps integrate the design work and provides a higher feasibility to explore a far wider range of architectural alternative (Reaz et al., 2007). In this study, to validate the effectiveness of the method, various text inputs have been used. The method provides a systematic approach for hardware realization, facilitating the rapid prototyping of boolean function classification schemes for lossless data compression.

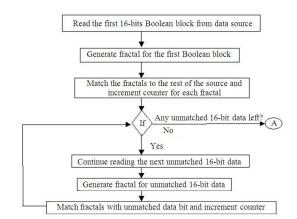

Algorithm development: In Boolean function classification algorithm, 16-bit of data bits are extracted from data input. The first 16-bit Boolean block is then used to generate fractal. The fractal is then used to match with the fractals for all other bits in the data source.

If there are identical matches between the first fractal with the fractals in the data source, the counter for the fractal is incremented. After, all the data bits are matched with the first fractal, the first unmatched 16-bit data will be used as the next fractal. This next fractal is matched with the remaining bits of data. Again, when there are matches between the second fractal with the data source, the counter for the second fractal will be incremented. The same algorithm continues until there is no more unmatched data source. Fig 1 shows the flow chart for the algorithm as explained.

Fig. 1: Boolean function classification algorithm

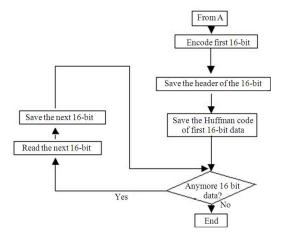

Fig. 2: Huffman encoding algorithm

Fig. 3: Decompression algorithm

When there is no more unmatched data source with the fractal, the algorithm continues with the Huffman encoding to compress the classified data source. From the counters for each of the fractals, the frequency of occurrence for each fractal can be determined. Based on Huffman algorithm (Reaz et al., 2004; Huffman, 1952; Mogaki et al., 2007), the data bits with higher number of occurrence are to be encoded with shorter codes, whereas the data bits with lower number of occurrence are to be encoded with longer codes. The same concept applies in this compression. For the fractal with higher number of occurrence, the fractal is encoded with a short code and saved with a header to enable the data to be retrieved or decompressed. This is to be explained in the decompression. Each of the fractals is encoded using Huffman encoding and this completes the Boolean compression. Fig 2 shows the flow chart for Huffman encoding algorithm.

The decompression algorithm involves rebuilding the Huffman tree from a stored frequency table in the header of the compressed file and converting or decompressing the bit streams of variable encode length into characters. Beginning at the root node based on the header stored in the compressed data and depending on the value of the bit, the right or left branch of the Huffman tree is taken and then return to read another bit for the next branch. When the node selected is a leaf, which means that it has no right and left child nodes, its character value is written to the decompressed file and goes back to the root node for the next bit. This algorithm is continued until all the compressed bits of variable encode length are decompressed. Figure 3 shows the decompression algorithm.

VHDL implementation: The design started with two blocks, compressor and decompressor. The input of the compressor is integer stream, where 8-bit binary data is read in as input for the compression. The data input is classified and compressed into another form. The classified data is shown in its respective class, which is represented by the 3-bit class output pin. The output data is a variable-length Huffman code, which is the compressed data. This compressed data is available from output pins. Each 8-bit data from the input will be compressed according to the look-up table built. The input data into the decompressor chip is a bit stream with length of 1-bit to 6-bit and the class of 3-bit. The output of the decompression is an 8-bit data.

VHDL modeling had been performed using the developed algorithm as discussed. The implementation

is started by building a statistical lookup table for all the possible text inputs, ranging from a to z for small case, A to Z for uppercase and some special characters like semicolon, each with specific class. An ASCII-tobinary program written in JavaScript is used to convert the text input into binary bits. The ASCII table for each of these characters is also referred. This ASCII table is used as a reference to specify the bit patterns for each of the input character. The bit patterns for each of the input character are important in the formation of the lookup table consisting of all possible text inputs. Since the compressor can recognize 71 characters, these characters are classified into their respective classes. After determining the size of the class, the next step is to determine the characteristic of the class. The equations to determine the class using definition for direct symmetric Boolean function is Eq. 1

$$f(z) = f(x, y) = f(y, x)$$

(1)

where, x is initialized to 001 and y = m-1, where m is the length of the encoded bits. x is initialized to 001 to represent the class for encoded data with length of 1 bit. Thus Eq. 2:

$$f(z) = f((001)2, (m-1)10) = f((m-1)10, (001)2)$$

(2)

For the function to be a direct symmetric function f(z) represents function for classification of the Boolean function derived using definition for direct symmetric Boolean function.

To perform the compression, the input data will first match with all the predefined inputs in the lookup table. When the input data is matched successfully, the length of the encoded output will be shown and the output will be displayed. The output is of variable length. Thus, careful declaration of the vector size is needed to ensure correct compilation and simulation. The possible length of the encoded output ranges from 1 bit to 6 bits, which is lesser than the uncompressed form of data for each character, which is 8 bits.

For the decompression of the encoded data, the class of the encoded data and the compressed data are used as the inputs to run the decompression program. Again, the compressed data may be of different length, which varies from 1-bit to 6-bit. The inserted class and compressed data will then be matched with all the predefined data in the lookup table. When the inserted class and compressed data matches with the predefined data in the lookup table, then the output, which is the original data before compression can be obtained.

| S (MAN-Halas II Ele Edit Ven Node Assign Unities Options Window Help . 8 > |        |                                          |               |              |               |               |  |  |

|----------------------------------------------------------------------------|--------|------------------------------------------|---------------|--------------|---------------|---------------|--|--|

|                                                                            |        | n ar |               |              | R Q           |               |  |  |

| Ref. 0.0ns                                                                 |        | •• Time: 2.68us                          | Interval: 2.6 | Bus          |               |               |  |  |

|                                                                            |        |                                          |               |              |               |               |  |  |

| Name:                                                                      | Value  | 2.0us 4.1                                | Ous 6.Ous     | 8.0us 10.0us | 12.0us 14.0us | 16.Dus 18.Dus |  |  |

| iiii)— clk                                                                 | 1      |                                          |               |              |               |               |  |  |

| 🗊 inputData                                                                | ·      | 00110101                                 | 00110110      | 00110111     | 01100011      | 00111001      |  |  |

| ilass 🖅                                                                    | B 100  | 100                                      | χ             | 100          | X             | 100           |  |  |

| outputData4                                                                | B 0000 | 0000                                     | χ 0001        | 0010         | 1001          | 0100          |  |  |

| ļ .                                                                        |        |                                          | ~             |              |               | _^            |  |  |

| ₿ <b>№</b>        | aresse                     | ila de ta                   |                                                                                                                |                                                        |

|-------------------|----------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| * *               | Time: 29.2us               | Interval: 29.2us            |                                                                                                                |                                                        |

|                   |                            |                             |                                                                                                                |                                                        |

| Value 20.0us      | 22.0us 24                  | .0us 26.0us 28.0u           | is 30.0us 31                                                                                                   | 2.0us 34.0us                                           |

| 1                 |                            |                             |                                                                                                                |                                                        |

| ι. <del>.</del> χ | 01101011                   | 01101100                    | 01110000                                                                                                       | 01110111                                               |

| B 100             | 100                        | ) 100 )                     | 100                                                                                                            | ( 100                                                  |

| B M Y             | 1000                       | γ 1011 γ                    | 0111                                                                                                           | γ 1110                                                 |

|                   | Value 20.0us<br>1<br>B 100 | Value 20.0us 22.0us 24<br>1 | Value 20.0x 24.0x Interval: 29.2x   Value 20.0x 24.0x 26.0x 28.0x   - 0.0101011 0.010100 0   B 100 100 100 100 | Value 20 Dus 22 Dus 24 Dus 26 Dus 28 Dus 30 Dus 31<br> |

Fig. 4: Simulation results for compression

| 🕅 MAX+plus II - d:\lecture notes\final year project\project_updated\project_updated\thesis\vhdl codes |                         |                    |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|-------------------------|--------------------|--|--|--|--|--|

| 🞇 MAX+plus II File Edit View Node Assign Utilities Options Window Help                                |                         |                    |  |  |  |  |  |

| DBB6 XD6                                                                                              | 1 <u>~ N AR5595</u>     | a Mee 7.7.2        |  |  |  |  |  |

| Start: 0.0ns                                                                                          | ♦ ♦ End: 80.0us         | Interval: 80.0us   |  |  |  |  |  |

| A                                                                                                     |                         |                    |  |  |  |  |  |

|                                                                                                       | Value 25.0us            | 30.0us 35.0us      |  |  |  |  |  |

| clk                                                                                                   |                         |                    |  |  |  |  |  |

| 📭 class 🛛 🖻                                                                                           | 3 100                   | 100                |  |  |  |  |  |

|                                                                                                       | 0000 1000 ( 1011 )      | 0111 ( 1110        |  |  |  |  |  |

| 🔍 🖅 inputData                                                                                         | - 01101011 ( 01101100 ) | 01110000 (01110111 |  |  |  |  |  |

| Θ                                                                                                     | (b)                     |                    |  |  |  |  |  |

Fig. 5: Simulation for decompression

Table 1: The Usage of Logic Resources in EPF10K10LC84-3

| LCs used              | 366 LCs out of 576 (63.54%) |

|-----------------------|-----------------------------|

| Number of nets        | 444                         |

| Number of inputs      | 1843                        |

| I/O cells             | 66                          |

| Cells in logic mode   | 323                         |

| Cells in cascade mode | 43                          |

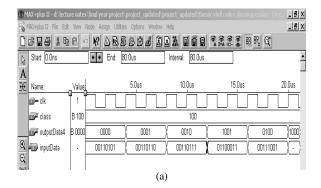

**Simulation:** The system was coded in IEEE-compliant VHDL and compiled and simulated using the MAX+PLUS2. This provides an opportunity to detect and correct errors early in the design process (Hunter, 1996; Ashenden, 2008). Both compression and decompression modules was designed and tested in isolation before being incorporated into the higher levels of the design.

Both compression and decompression modules were first simulated individually to verify their functionalities. Each module was fed a fix inputs and the correct outputs were observed. After the successful individual simulations were performed, the modules were integrated together. This enables detailed simulation at the top level.

The results are generated using waveform editor. The clock signal and outputs are shown in the timing diagram. Few example simulations are shown in Fig. 4 and 5 using the 72-bit input binary data.

Compression simulation: In Fig. 4, the generated data inputs are 00110101, 00110110, 00110111, 01100011, 00111001, 01101011, 01101100, 01110000 and 01110111. The encoded outputs are 0000, 0001, 0010, 1001, 0100, 1000, 1011, 0111 and 1110. The outputs are the same as the output in the lookup table. This vields that the compression is performed correctly. In this simulation, the compression ratio is 50%. The best compression ratio for this algorithm is 87.5%, which is the case when all the inputs are having encoded output of 1 bit. However, this rarely occurs since text inputs usually consist of various different characters, which have their respective class and output bits as defined in the lookup table. The average compression ratio is 25-37.5% from numerous testing with various text inputs. This is verified from the lookup table as well, since class 101 and class 110 have most input texts and their encoded bits range from 5 bits to 6 bits.

**Decompression simulation:** In Fig. 5, the input is the compressed data and class. The compressed data are 0000, 0001, 0010, 1001, 0100, 1000, 1011, 0111 and 1110. The outputs are 00110101, 00110110, 00110111, 01100011, 001110001, 01110001, 01101010, 01110000 and 01110111. The outputs are exactly the original inputs, which verify the correct functionalities of the algorithm.

**Synthesis:** Concerning the designated hardware realization, The VHDL code is synthesized by considering Altera FLEX10K: EPF10K10LC84-3 FPGA chip on LC84 package. The physical hardware layout is generated using the synthesis tool Synplify

version 7.0. The FLEX 10 K families provide the density, speed and features to integrate entire systems, including multiple 32-bit buses into a single chip. A comparatively low critical path frequency was achieved which was 27.9 MHz. The design took a minimum resource i.e., 366 logic cells, which is 63.54% of the device EPF10K10LC84. Table 1 shows a details report of the usage of resources.

## CONCLUSION

The objective of this project was to hardware prototyping of Boolean compression algorithm using VHDL. The Boolean function classification schemes are incorporated into Huffman coding for a better compression algorithm. The modules were successfully compiled, simulated and synthesized with achieved maximum frequency of 27.9 MHz and a minimum resource usage of 63.5% of the total cells. The hardware implementation demonstrated complete, correct functionality and met all the initial system requirements.

## REFERENCES

- Akter, M., M.B.I. Reaz, F. Mohd-Yasin and F. Choong, 2008. Hardware implementations of an image compressor for mobile communications. J. Commun. Technol. Electr., 53: 899-910. DOI: 10.1134/S106422690808007X

- Amin, M.S., M. Mamun, F.H. Hashim, J. Jalil and H. Husain, 2011. Design and implementation of novel artificial neural network based stock market forecasting system on field-programmable gate arrays. Am. J. Applied Sci., 8: 1054-1060. DOI: 10.3844/ajassp.2011.1054.1060

- Ashenden, P.J., 2008. The Designer's Guide to VHDL. 3rd Edn., Morgan Kaufmann, San Francisco, ISBN-10: 0120887851, pp: 909.

- Chang, C.H. and B.J. Falkowski, 1996. Operations on boolean functions and variables in spectral domain of arithmetic transform. Proceedings of the IEEE International Symposium on Circuits and Systems, May 12-15, IEEE Xplore Press, Atlanta, GA, USA., pp: 400-403. DOI: 10.1109/ISCAS.1996.541986

- Choong, F., M.B.I. Reaz and F. Mohd-Yasin, 2005. Power quality disturbance detection using artificial intelligence: A hardware approach. Proceedings of the 19th IEEE International Parallel and Distributed Processing Symposium, Apr. 4-8, IEEE Xplore Press, Denver, USA., pp: 146a-146a. DOI: 10.1109/IPDPS.2005.348

- Choong, F., M.B.L. Reaz, T.C. Chin and F. Mohd-Yasin, 2006. Design and implementation of a data compression scheme: A partial matching approach. Proceedings of the International Conference on Computer Graphics, Imaging and Visualisation, Jul. 26-28, IEEE Xplore Press, Sydney, Qld., pp: 150-155. DOI: 10.1109/CGIV.2006.94

- Coussy, P., D.D. Gajski, M. Meredith and A. Takach, 2009. An introduction to high-level synthesis. IEEE Design Test Comput., 26: 8-17. DOI: 10.1109/MDT.2009.69

- Huffman, D.A., 1952. A method for the construction of minimum-redundancy codes. Proc. IRE, 40: 1098-1101. DOI: 10.1109/JRPROC.1952.273898

- Hunter, R.D.M. and T.T. Johnson, 1996. Introduction to VHDL. 1st Edn., Springer, London, ISBN: 0412731304, pp: 482.

- Marufuzzaman, M., M.B.I. Reaz, M.S. Rahman and M.A.M. Ali, 2010. Hardware prototyping of an intelligent current dq PI controller for FOC PMSM Drive. Proceedings of the International Conference on Electrical and Computer Engineering, Dec. 18-20, IEEE Xplore Press, Dhaka, pp: 86-88. DOI: 10.1109/ICELCE.2010.5700559

- Mogaki, S., M. Kamada, T. Yonekura, S. Okamoto and Y. Ohtaki *et al.*, 2007. Time-stamp service makes real-time gaming cheat-free. Proceedings of the 6th ACM SIGCOMM Workshop on Network and System Support for Games, (NSSG' 07), ACM, New York, USA., pp: 135-138. DOI: 10.1145/1326257.1326281

- Mohd-Yasin, F., A.L. Tan and M.I. Reaz, 2004. The FPGA prototyping of iris recognition for biometric identification employing neural network. Proceedings of the 16th International Conference on Microelectronics, Dec 6-8, IEEE Xplore Press, Malaysia, pp: 458-461. DOI: 10.1109/ICM.2004.1434697

- Reaz, M.B.I., M.T. Islam, M.S. Sulaiman, M.A.M. Ali and H. Sarwar et al., 2003. FPGA realization of multipurpose FIR filter. Proceedings of the 4th International Conferecne Parallel on and Distributed Computing, Applications and Technologies, Aug. 27-29, IEEE Xplore Press, Malaysia, 912-915. DOI: pp: 10.1109/PDCAT.2003.1236448

- Reaz, M.B.I., M.S. Sulaiman, F.M. Yasin and T.A. Leng, 2004. IRIS recognition using neural network based on VHDL prototyping. Proceedings of the 2004 International Conference on Information and Communication Technologies: From Theory to Applications, Apr. 19-23, IEEE Xplore Press, Malaysia, pp: 463-464. DOI: 10.1109/ICTTA.2004.1307832

- Reaz, M.B.I., F. Mohd-Yasin, S.L. Tan, H.Y. Tan and M.I. Ibrahimy, 2005. Partial encryption of compressed images employing FPGA. Proceedings of the IEEE International Symposium on Circuits and Systems, May 23-26, IEEE Xplore Press, Malaysia, pp: 2385-2388. DOI: 10.1109/ISCAS.2005.1465105

- Reaz, M.B.I., F. Choong and F. Mohd-Yasin, 2006. VHDL modeling for classification of power quality disturbance employing wavelet transform, artificial neural network and fuzzy logic. Simulation, 82: 867-881. DOI: 10.1177/0037549707077782

- Reaz, M.B.I., F. Choong, M.S. Sulaiman and F. Mohd-Yasin, 2007. Prototyping of wavelet transform, artificial neural network and fuzzy logic for power quality disturbance classifier. J. Electric Power Components Syst., 35: 1-17. DOI: 10.1080/15325000600815431

- Reaz, M.B.I., M.I. Ibrahimy, F. Mohd-Yasin, C.S. Wei and M. Kamada, 2007. Single core hardware module to implement encryption in TECB mode. Informacije MIDEM, LJUBLJANA, 37: 165-171.

- Reaz, M.B.I., J. Jalil, H. Husain and B. Bais, 2011b. Subway train braking system: A fuzzy based hardware approach. Am. J. Applied Sci., 8: 740-747. DOI: 10.3844/ajassp.2011.740.747

- Reaz, M.B.I., M.S. Amin, F.H. Hashim and K. Asaduzzaman, 2011a. Single core hardware module to implement partial encryption of compressed image. Am. J. Applied Sci., 8: 566-573. DOI: 10.3844/ajassp.2011.566.573

- Tsai, C.C. and M. Marek-Sadowska, 1997. Boolean functions classification via fixed polarity reedmuller forms. IEEE Trans. Comput., 46: 173-186. DOI: 10.1109/12.565592

- Visweswariah, K., S.R. Kulkarni and S. Verdu, 2000. Universal coding of nonstationary sources. IEEE Trans. Inform. Theory, 46: 633-1637. DOI: 10.1109/18.850707